## **DIRECT WAFER BONDING AT LETI**

Leti Innovation Days | June 28-29, 2017

Frank Fournel

Head of wafer bonding engineering

#### **DIRECT WAFER BONDING**

## "spontaneous bonding at room temperature without polymer"

- Versatile process

- Mass production demonstrated

- μelectronics and μtechnology processes compatibility

- Could be a low temperature process

**Surface preparations**

Critical surface preparations (roughness, flatness, defect level...)

### **Bonding**

#### **DIRECT WAFER BONDING**

# "spontaneous bonding at room temperature without polymer"

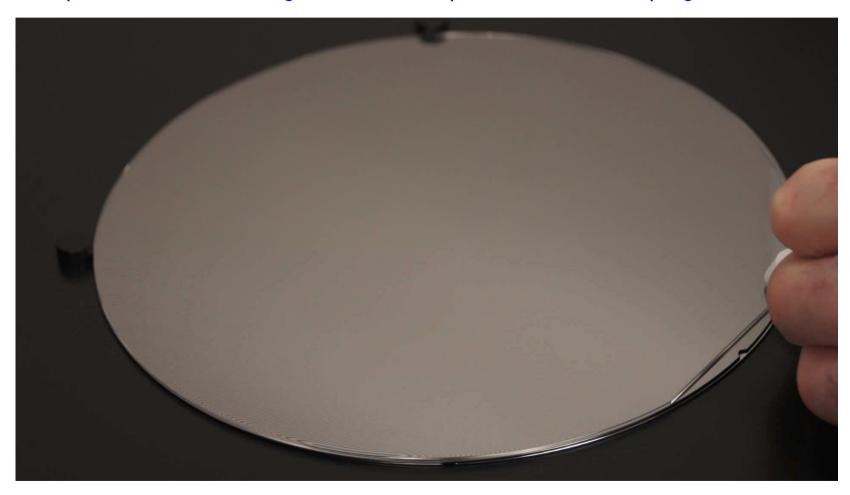

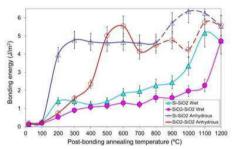

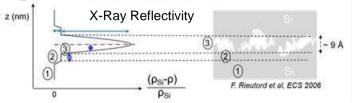

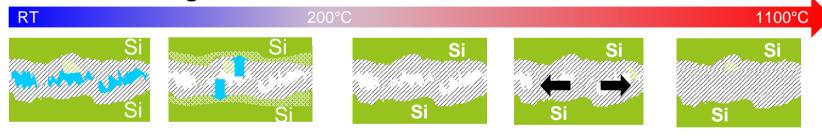

#### SILICON DIRECT WAFER BONDING

Direct bonding studies

Direct bonding mechanisms (rough surface model with water management)

Some realizations

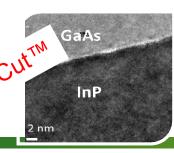

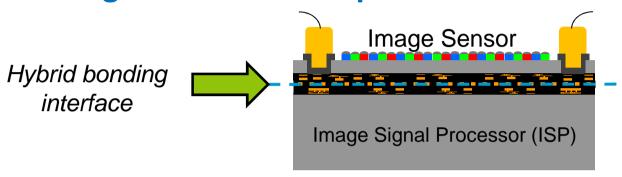

#### HYBRID DIRECT WAFER BONDING

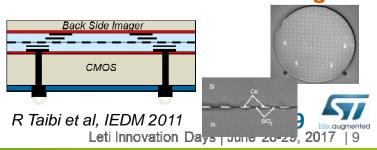

### New 3D imager sensor development with W2W hybrid bonding

**STMicroelectronics** & LETI collaboration

**Direct hybrid bonding of BEOLs levels**

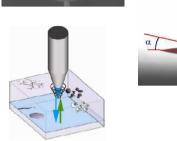

#### Surface preparation improvement

#### **HYBRID DIRECT WAFER BONDING**

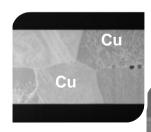

## **Hybrid bonding**

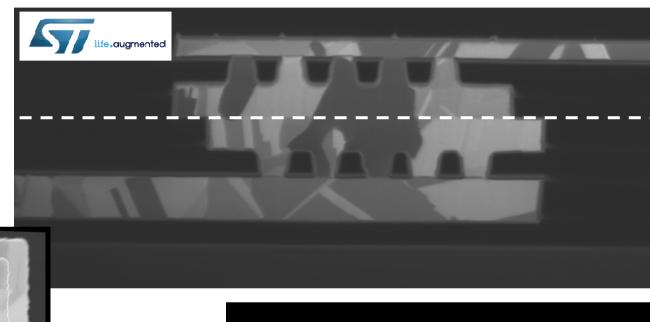

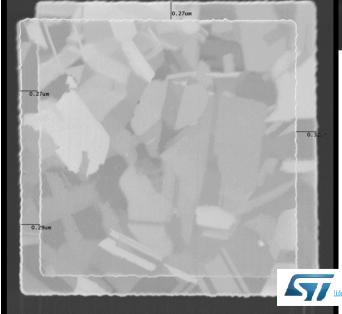

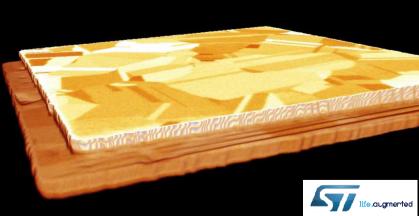

Typical Cu/Cu bonding pad with Cu crystal growth during bonding interface disappearance.

#### **HYBRID DIRECT WAFER BONDING**

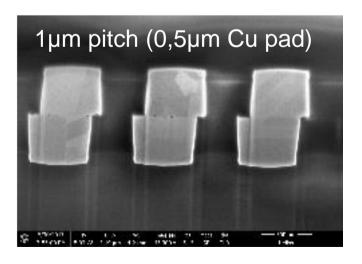

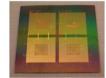

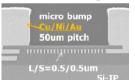

## Fine pitch

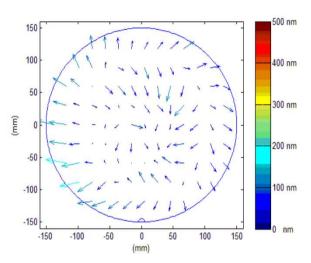

Post-bonding SAM characterization

Global alignment: 10nm @ 3σ 195 nm

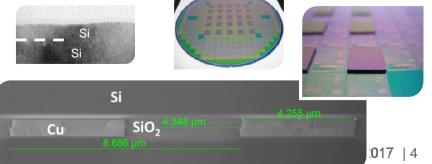

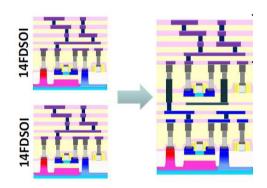

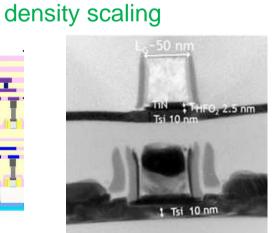

#### DIRECT WAFER BONDING FOR MOORE LAW

**SOI** Substrates Mobility booster (sSOI, GeOI, ...) **Ultrathin Buried Oxide** Alternatives Buried Oxide (SiNx, C\*, ...)

Monolithic 3D for further

P. Batude, VLSI 2011

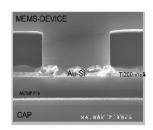

#### AND ENABLING MORE THAN MOORE...

Hermetic Wafer Level **Packaging** S. Nicolas et al, ECTC 2017

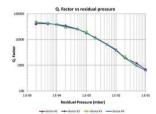

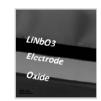

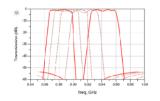

#### High performances RF **Filters**

Piezoelectric thin film transfer

JS Moulet et al, IEDM 2008 B. Imbert, IFCS 2011 Undisclosed industrial partner Dutoit et al., VLSI Circuits 2013

**Applications**

#### High density 3D Silicon Interposer

J. Charbonnier et al., ESTC 2012, ECTC 2013

#### 3D stacked CMOS imager

#### **CEA-LETI BONDING ECOSYSTEM**

Fundamental research through academic collaborations

- R&D partnership with

- Soitec (20 years long collaboration)

Industrial equipment suppliers collaboration

- More than 60 patents related to bonding tech. and app.

- International recognition with conference board

- ECS (Wafer bond symposium), Wafer bond conference, EEE S3S conference ...

## Thank you!

#### Leti, technology research institute

Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 rue des Martyrs | 38054 Grenoble Cedex | France www.leti-cea.com